ターゲット

公開日

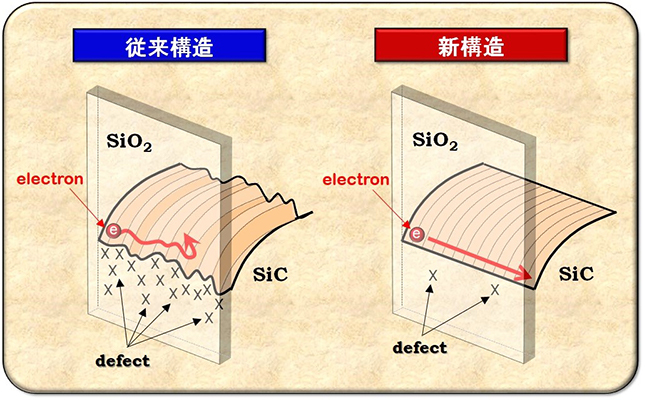

木本恒暢 工学研究科教授、立木馨大 同博士後期課程学生らの研究グループは、省エネの切り札と言われるSiC(シリコンカーバイド)半導体で問題になっていた欠陥(不完全性)を独自の手法で大幅に低減し、実用的な構造でSiCトランジスタの性能を6倍以上向上することに成功しました。

Si(シリコン)を中心とした半導体は、計算機のロジックやメモリだけでなく、電気自動車、電車のモータ制御、電源などに広く用いられていますが、消費電力(電力損失)が大きな問題となっています。近年、低損失化を目指して、Siよりも性質の優れたSiCによるトランジスタ開発が活発になり、実用化が始まりました。

しかしSiCトランジスタの心臓部となる酸化膜とSiCの境界部分(界面)に多くの欠陥が存在し、SiC本来の性能を発揮できない状況が20年以上続いていました。本研究グループは、昨年、物理的考察に基づく独自の手法により界面の欠陥を大幅に低減し、SiCトランジスタの性能が2倍向上することを報告しました。今回、この研究をさらに発展させ、実用的に重要な構造においてSiCトランジスタの性能を6~80倍向上させることに成功しました。今回の技術により、普及が進む電気自動車や産業機器などへの、低損失SiCデバイス適用が急速に拡大し、エネルギー問題にも大きく貢献できます。

本研究成果は、2021年10月26日に、SiC半導体に関するヨーロッパ会議(ECSCRM)で発表されます。

詳しい研究内容について

研究者情報

研究者名

木本 恒暢

メディア掲載情報

日刊工業新聞(10月27日 23面)に掲載されました。

関連部局