2013年6月18日

左から小野教授、Kim助教

小野輝男 化学研究所教授、小林研介 大阪大学教授(元同准教授)、千葉大地 東京大学准教授(元同准教授)、Kim Kab-Jin 同助教、小山知弘 東京大学助教(元同大学院生)、上田浩平氏、平松亮氏、吉村瑶子氏(以上、同大学院生)は、仲谷栄伸 電気通信大学教授、大野英男 東北大学教授、山ノ内路彦 同助教、深見俊輔 同博士、河野浩 大阪大学准教授、多々良源 理化学研究所チームリーダーとの共同研究で、強磁性ナノ細線における磁壁移動の閾値を決める障壁が、電流と磁場で全く異なることを見いだし、その定量評価に成功しました。磁気記録デバイスの低消費電力化への寄与が期待できる成果であり、応用上の観点からも特筆すべきことです。

この成果は、英国科学誌Nature Communications誌に2013年6月17日(英国時間)にオンライン公開されました。

背景

ハードディスクドライブなどの記録装置では、磁石の向きで情報を蓄えています。これらの装置では、磁石の向きを変えて情報を書き込み、その向きを検知して情報が読み取られます。記録密度が上がって情報である磁石の大きさが小さくなると、室温の熱エネルギーによって磁石の向きが変わってしまい、情報がなくなってしまうという問題が出てきました。このため小さな磁石でも向きが変わりにくい材料を開発する努力がなされてきました。しかし、このような向きが変わりにくい磁石の向きを変えて情報を書き込むには大きな電力が必要になります。現在、この情報保持の安定性と低消費電力化が両立しないというジレンマが大きな問題となっています。

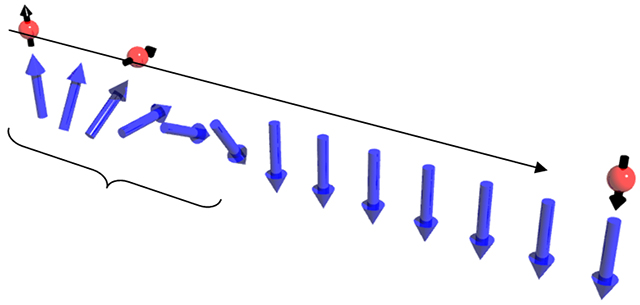

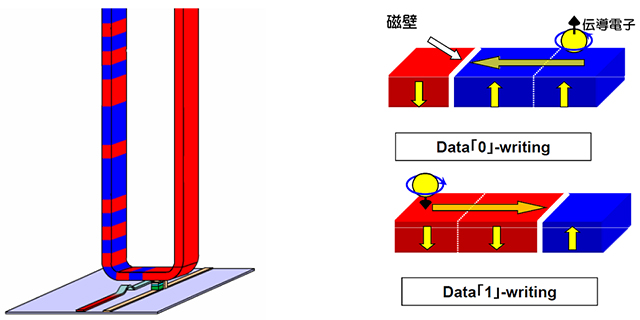

強磁性体の磁区と磁区の境界を磁壁と呼びます(図1)。磁壁はナノスケールの磁化のねじれ構造で、これを電流で移動させることが可能であることを本学の研究グループが2004年に示しました(Phys. Rev. Lett., 92 (2004) 077205)。その後、この現象を利用した新規メモリ素子がIBMやNECにより提案されました(図2)。これらの新規メモリは、半導体メモリを凌駕する大容量性・高速性・低い消費電力を兼ね備えた廉価な不揮発性磁気メモリとして期待されています。これまで精力的な研究が行われてきましたが、これらのデバイスでも情報保持の安定性と低消費電力化を両立するのは困難と考えられてきました。

図1:磁壁の概念図。磁壁内部では磁化がねじれた構造をとっている。スピン偏極した伝導電子(スピン偏極電流)を流すと、磁壁内部の磁化はトルクを受け、磁壁全体が電流と逆方向(伝導電子の流れの向き)に移動する。

図2:IBM(左)とNEC(右)によって提案された電流による磁壁駆動を用いた不揮発性メモリの概念図。IBMの提案したメモリはレーストラック型メモリと呼ばれ、0と1の情報が書き込まれた磁性細線中の磁壁を電流で駆動して所望のデータを読み出す手法を用いる。NECにより提案されたメモリは中央の磁化方向を電流磁壁駆動によりスイッチさせデータを書き込む。

研究手法と成果

研究チームは、コバルトとニッケルを積層した強磁性薄膜を100ナノメートル程度の幅の細線に加工し、細線中の磁壁を電流や磁場で駆動する実験を室温で行いました。

磁壁を電流や磁場で動かす時に動き出す閾値を、閾電流、閾磁場と定義します。閾磁場は細線エッジの凸凹や欠陥などの外因的な要因(外因性ピンニング)で決まることが知られていて、その値から磁壁に対するエネルギー障壁(ピニングポテンシャル)の大きさが評価されます。

研究チームは、閾電流からも磁壁に対するエネルギー障壁の大きさを評価できることを示し、その大きさを定量的に見積もりました。

驚いたことに、得られた磁壁に対するエネルギー障壁の大きさは磁場の場合と電流の場合で大きく異なっていました。具体的には、磁場に対しては室温のエネルギーの400倍程度、電流に対しては60倍程度でした。これらの結果は、磁壁を磁場で駆動する場合と電流で駆動する場合の2種類のエネルギー障壁があることを示しています。

また、理論的考察から、磁場に対するエネルギー障壁が情報安定性を決め、電流に対するエネルギー障壁が磁壁の移動しやすさ(消費電力)を決めるということが分かりました。これらのエネルギー障壁は試料形状や材料特性で独立に制御することが可能であると考えられ、独立した2種類の障壁を利用することで情報保持の安定性と低消費電力化の両立が可能であると期待されます。さらに、室温エネルギーの60倍の障壁によって10年の記録保持が可能であることが分かっており、実験で得られた室温エネルギーの400倍の障壁は応用上も十分な大きさであることも明らかとなりました。

本研究の一部は、科学研究費補助金基盤研究(S)「新規スピンダイナミクスデバイスの研究」、最先端研究開発支援プログラム「省エネルギー・スピントロニクス論理集積回路の研究開発」、および化学研究所共同利用・共同研究課題によって支援されました。

参考文献

(IBM):Parkin, S. S. P., Hayashi, M. & Thomas, L. Magnetic domain-wall racetrack memory. Science 320, 190 (2008).

(NEC):Fukami, S. et al. Low-current perpendicular domain wall motion cell for scalable high-speed MRAM. 2009 symposiumon VLSI technology. Digest Tech. 24 Pap. 230 (2009).

書誌情報

[DOI] http://dx.doi.org/10.1038/ncomms3011

Kim Kab-Jin, Hiramatsu Ryo, Koyama Tomohiro, Ueda Kohei, Yoshimura Yoko, Chiba Daichi, Kobayashi Kensuke, Nakatani Yoshinobu, Fukami Shunsuke, Yamanouchi Michihiko, Ohno Hideo, Kohno Hiroshi, Tatara Gen, Ono Teruo.

Two-barrier stability that allows low-power operation in current-induced domain-wall motion.

Nature Communications 4, Article number: 2011, 2013/06/17/online

- 京都新聞(6月18日 23面)および日刊工業新聞(6月18日 23面)に掲載されました。